ISO IEC 15776 Klausa 1.1 – 1.3 adalah Standar Internasional mengenai VME64bus Specification, yang mendefinisikan sistem antarmuka yang digunakan untuk menghubungkan mikroprosesor, penyimpanan data, dan perangkat kontrol periferal.

Artikel ini merupakan lanjutan dari artikel sebelumnya berikut :

- ISO IEC 15776 VME64bus Specification

Standar ISO 15776 Klausa 1.1 – 1.3

1. General : Umum

1.1 Scope and object : Lingkup dan objek

Spesifikasi VMEbus mendefinisikan sistem antarmuka yang digunakan untuk menghubungkan mikroprosesor, penyimpanan data, dan perangkat kontrol periferal dalam konfigurasi perangkat keras yang digabungkan.

Sistem ini dibuat dengan tujuan sebagai berikut:

- a) untuk memungkinkan komunikasi antar perangkat di VMEbus tanpa mengganggu aktivitas internal perangkat lain yang terhubung ke VMEbus;

- b) untuk menentukan karakteristik sistem elektrik dan mekanik yang diperlukan untuk merancang perangkat yang akan berkomunikasi secara andal dan jelas dengan perangkat lain yang dihubungkan ke VMEbus;

- c) untuk menentukan protokol yang secara tepat mendefinisikan interaksi antara VMEbus dan perangkat yang dihubungkan dengannya;

- d) untuk memberikan terminologi dan definisi yang menjelaskan protokol sistem;

- e) untuk memungkinkan rentang yang luas dari garis lintang desain sehingga perancang dapat mengoptimalkan biaya dan/atau kinerja tanpa mempengaruhi kompatibilitas sistem;

- f) untuk menyediakan sistem di mana kinerja terutama terbatas pada perangkat, daripada antarmuka sistem terbatas.

1.2 Normative references : Referensi normatif

Dokumen referensi berikut sangat diperlukan untuk penerapan dokumen ini. Untuk referensi bertanggal, hanya edisi yang dikutip yang berlaku.

Untuk referensi yang tidak bertanggal, berlaku edisi terbaru dari dokumen yang diacu (termasuk amandemennya).

- IEC 60297-1:1986, Dimensions of mechanical structures of the 482,6 mm (19 in) series — Part 1: Panels and racks

- IEC 60297-2:1982, Dimensions of mechanical structures of the 482,6 mm (19 in) series — Part 2: Cabinets and pitches of rack structures

- IEC 60297-3:1984, Dimensions of mechanical structures of the 482,6 mm (19 in) series — Part 3: Subracks and associated plug-in units

- IEC 60297-4:1995, Mechanical structures for electronic equipment — Dimensions of mechanical structures of the 482,6 mm (19 in) series — Part 4: Subracks and associated plug-in units — Additional dimensions

- IEC 60603-2:1995, Connectors for frequencies below 3 MHz for use with printed boards — Part 2: Detail specification for two-part connectors with assessed quality, for printed boards, for basic grid of 2.54 mm (0.1 in) with common mounting features

- IEC 61076 (all parts), Connectors with assessed quality, for use in d.c., low frequency analogue and digital high speed data applications

- IEEE 1101.2, Standard for Mechanical Core Specifications for Conduction-Cooled Eurocards

- IEEE 1394, Standard for a High Performance Serial Bus.

1.3 VMEbus interface system elements : elemen sistem antarmuka VMEbus

1.3.1 Basic definitions : Definisi dasar

Struktur VMEbus dapat digambarkan dari dua sudut pandang: struktur mekanik dan struktur fungsionalnya.

Spesifikasi mekanis menjelaskan dimensi fisik subrak, bidang belakang, panel depan, board (papan) plug-in, dll.

Spesifikasi fungsional VMEbus menjelaskan cara kerja bus, modul fungsional apa yang terlibat dalam setiap transaksi, dan aturan yang mengatur perilakunya.

Definisi informal berikut menjelaskan beberapa istilah dasar yang digunakan untuk struktur mekanis dan fungsional VMEbus.

1.3.1.1 VMEbus mechanical structure : Struktur mekanik VMEbus

1.3.1.1.1 VMEbus backplane : Pesawat belakang VMEbus

board (papan) sirkuit tercetak (PC) dengan konektor 96 atau 160 pin dan jalur sinyal yang menghubungkan pin konektor

Beberapa sistem VMEbus memiliki satu board (papan) PC, yang disebut backplane J1.

Ini menyediakan jalur sinyal yang diperlukan untuk operasi dasar.

Sistem VMEbus lainnya juga memiliki board (papan) PC kedua opsional, yang disebut backplane J2.

Ini menyediakan konektor 96 atau 160 pin tambahan dan jalur sinyal yang diperlukan untuk transfer data dan alamat yang lebih luas.

Yang lain lagi memiliki board (papan) PC tunggal yang menyediakan konduktor sinyal dan konektor dari kedua backplanes J1 dan J2.

1.3.1.1.2 board : board (papan)

board (papan) sirkuit tercetak (PC), kumpulan komponen elektroniknya, dengan satu atau dua konektor 96 atau 160 pin yang dapat dipasang ke konektor backplane VMEbus

1.3.1.1.3 slot : slot

posisi di mana board (papan) dapat dimasukkan ke backplane VMEbus

Jika sistem VMEbus memiliki backplane J1 dan J2 (atau kombinasi backplane J1/J2), setiap slot menyediakan sepasang konektor 96 atau 160 pin. Jika sistem hanya memiliki bidang belakang J1, maka setiap slot menyediakan konektor tunggal 96 atau 160 pin.

1.3.1.1.4 subrack : subrak

kerangka kaku yang memberikan dukungan mekanis untuk board (papan) yang dimasukkan ke bidang belakang, memastikan bahwa konektor berpasangan dengan benar dan board (papan) yang berdekatan tidak saling bersentuhan.

Ini juga memandu aliran udara pendingin melalui sistem, dan memastikan bahwa board (papan) yang dimasukkan tidak terlepas dari bidang belakang karena getaran atau guncangan.

1.3.1.2 VMEbus functional structure : Struktur fungsional VMEbus

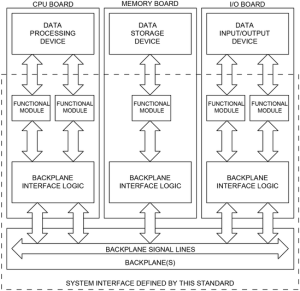

Gambar 1 menunjukkan diagram blok yang disederhanakan dari struktur fungsional, termasuk jalur sinyal VMEbus, logika antarmuka backplane, dan modul fungsional.

Klausa 1.3.1.2.1 – 1.3.1.2.8

1.3.1.2.1 backplane interface logic : logika antarmuka backplane

logika antarmuka khusus yang memperhitungkan karakteristik bidang belakang: impedansi saluran sinyalnya, waktu propagasi, nilai terminasi, dll.

Spesifikasi VMEbus menetapkan aturan tertentu untuk desain logika ini berdasarkan panjang maksimum bidang belakang dan jumlah slot board (papan) maksimumnya.

1.3.1.2.2 functional module : modul fungsional

kumpulan sirkuit elektronik yang berada di satu board (papan) VMEbus dan bekerja sama untuk menyelesaikan tugas

1.3.1.2.3 data transfer bus : bus transfer data

salah satu dari empat bus yang disediakan oleh backplane VMEbus

Bus Transfer Data memungkinkan Master untuk mengarahkan transfer data biner antara mereka dan Slave. (Data Transfer Bus sering disingkat DTB.)

1.3.1.2.4 data transfer bus cycle : siklus bus transfer data

urutan transisi level pada jalur sinyal DTB yang menghasilkan transfer alamat atau alamat dan data antara Master dan Slave

Siklus Bus Transfer Data dibagi menjadi dua bagian, siaran alamat dan kemudian nol atau lebih transfer data. Ada 34 jenis siklus Bus Transfer Data.

Mereka didefinisikan nanti dalam bab ini.

1.3.1.2.5 master : menguasai

modul fungsional yang memulai siklus DTB untuk mentransfer data antara dirinya dan modul Slave

Gambar 1 — System elements : Elemen sistem

1.3.1.2.6 slave : budak

modul fungsional yang mendeteksi siklus DTB yang diprakarsai oleh Master dan, ketika siklus tersebut menentukan partisipasinya, mentransfer data antara dirinya dan Master

1.3.1.2.7 location monitor : pemantau lokasi

modul fungsional yang memantau transfer data melalui DTB untuk mendeteksi akses ke lokasi yang telah ditetapkan untuk ditonton.

Ketika akses ke salah satu lokasi yang ditetapkan ini terjadi, Monitor Lokasi menghasilkan sinyal on-board

1.3.1.2.8 bus timer : pengatur waktu bus

modul fungsional dengan periode time-out preset yang mengakhiri siklus DTB jika transfer melebihi periode time-out.

Tanpa modul ini, jika Master mencoba mentransfer data ke atau dari lokasi Slave yang tidak ada, mungkin akan menunggu selamanya.

Pengatur Waktu Bus mencegah hal ini dengan menghentikan siklus

Klausa 1.3.1.2.9 – 1.3.1.2.18

1.3.1.2.9 priority interrupt bus : bus interupsi prioritas

salah satu dari empat bus yang disediakan oleh backplane VMEbus

Priority Interrupt Bus memungkinkan modul Interrupter untuk mengirim permintaan interupsi ke Interrupt Handler.

1.3.1.2.10 interrupter : pengganggu

modul fungsional yang menghasilkan permintaan interupsi pada Bus Interupsi Prioritas dan kemudian memberikan informasi Status/ID ketika Penangan Interupsi memintanya

1.3.1.2.11 interrupt handler : penangan interupsi

modul fungsional yang mendeteksi permintaan interupsi yang dihasilkan oleh Interrupter dan merespons permintaan tersebut dengan meminta informasi Status/ID.

1.3.1.2.12 status/ID

nilai delapan, enam belas, atau tiga puluh dua bit yang dikembalikan oleh pengganggu ke penangan interupsi selama siklus pengakuan interupsi

1.3.1.2.13 daisy-chain

jenis khusus jalur sinyal VMEbus yang digunakan untuk menyebarkan level sinyal dari board (papan) ke board (papan), dimulai dengan slot pertama dan diakhiri dengan slot terakhir

Ada empat rantai daisy hibah bus dan satu interupsi mengakui rantai daisy di VMEbus.

1.3.1.2.14 IACK daisy-chain driver : Driver rantai daisy IACK

modul fungsional yang mengaktifkan interupsi mengakui daisy-chain setiap kali Interrupt Handler mengakui permintaan interupsi

Daisy-chain ini memastikan bahwa hanya satu Interrupter yang akan merespons dengan STATUS/ID-nya ketika lebih dari satu telah menghasilkan permintaan interupsi.

1.3.1.2.15 arbitration bus : bus arbitrase

salah satu dari empat bus yang disediakan oleh backplane VMEbus

Bus ini memungkinkan modul Arbiter dan beberapa modul Pemohon untuk mengoordinasikan penggunaan DTB.

1.3.1.2.16 requester : peminta

modul fungsional yang berada di board (papan) yang sama dengan Master atau Interrupt Handler dan meminta penggunaan DTB kapan pun Master atau Interrupt Handler membutuhkannya

1.3.1.2.17 arbiter

modul fungsional yang menerima permintaan bus dari modul Peminta dan memberikan kontrol DTB ke satu Pemohon pada satu waktu

1.3.1.2.18 utility bus : bus utilitas

salah satu dari empat bus yang disediakan oleh backplane VMEbus

Bus ini termasuk sinyal yang menyediakan waktu periodik dan mengkoordinasikan power-up dan power-down sistem VMEbus.

Klausa 1.3.1.2.19 – 1.3.1.2.23

1.3.1.2.19 CR/CSR

modul fungsional yang menyediakan informasi ROM Konfigurasi dan Register Kontrol dan Status. Modul ini menyediakan ID manufaktur dan board (papan) serta informasi board (papan) penting lainnya

CSR digunakan untuk konfigurasi perangkat lunak sistem VMEbus.

1.3.1.2.20 system clock driver : driver jam sistem

modul fungsional yang menyediakan sinyal waktu 16 MHz pada Bus Utilitas

1.3.1.2.21 serial bus : bus serial

modul fungsional yang menyediakan antarmuka 2 kabel bus antar kartu di bidang belakang, terlepas dari modul VMEbus lainnya

1.3.1.2.22 power monitor module : modul monitor daya

modul fungsional yang memantau status sumber daya utama ke sistem VMEbus, dan memberi sinyal ketika daya itu menyimpang di luar batas yang diperlukan untuk pengoperasian sistem yang andal

Karena sebagian besar sistem ditenagai oleh a.c. sumber daya, Monitor Daya biasanya dirancang untuk mendeteksi kondisi putus atau rusak pada saluran AC.

1.3.1.2.23 system controller board : board (papan) pengontrol sistem

board (papan) yang berada di slot 1 dari backplane VMEbus dan memiliki System Clock Driver, Arbiter, IACK Daisy-Chain Driver, dan Bus Timer; beberapa juga memiliki Power Monitor

1.3.1.3 Types of cycles on the VMEbus : Jenis siklus pada VMEbus

Klausa 1.3.1.3.1 – 1.3.1.3.2

1.3.1.3.1 read cycle : membaca siklus

siklus DTB yang digunakan untuk mentransfer 1, 2, 3, 4 atau 8 byte dari Slave ke Master

Siklus dimulai ketika Master menyiarkan alamat dan pengubah alamat.

Setiap Slave menangkap pengubah alamat dan alamat dan memeriksa untuk melihat apakah itu merespons siklus.

Jika demikian, ia mengambil data dari penyimpanan internalnya, menempatkannya di bus data dan mengakui transfernya.

Master kemudian mengakhiri siklus.

1.3.1.3.2 write cycle : siklus tulis

siklus DTB yang digunakan untuk mentransfer 1, 2, 3, 4 atau 8 byte dari Master ke Slave

Siklus dimulai ketika Master menyiarkan alamat dan pengubah alamat dan menempatkan data pada DTB.

Setiap Slave menangkap alamat dan pengubah alamat dan memeriksa untuk melihat apakah itu merespons siklus.

Jika demikian, ia menyimpan data dan kemudian mengakui transfer. Master kemudian mengakhiri siklus.

Klausa 1.3.1.3.3 – 1.3.1.3.4

1.3.1.3.3 block read cycle : blokir siklus baca

siklus DTB yang digunakan untuk mentransfer blok 1 hingga 256 byte dari Slave ke Master

Transfer ini dilakukan dengan menggunakan string transfer data 1, 2, atau 4 byte. Setelah transfer blok dimulai, Master tidak melepaskan DTB sampai semua byte telah ditransfer.

Ini berbeda dari serangkaian siklus baca di mana Master hanya menyiarkan satu alamat dan pengubah alamat (di awal siklus).

Kemudian Slave menambah alamat ini pada setiap transfer sehingga data untuk transfer berikutnya diambil dari lokasi berikutnya yang lebih tinggi.

1.3.1.3.4 block write cycle : blok siklus tulis

siklus DTB yang digunakan untuk mentransfer blok 1 hingga 256 byte dari Master ke Slave.

Siklus penulisan blok sangat mirip dengan siklus baca blok.

Ini menggunakan string transfer data 1, 2, atau 4 byte. Master tidak melepaskan DTB sampai semua byte telah ditransfer.

Ini berbeda dari serangkaian siklus tulis di mana Master hanya menyiarkan satu alamat dan pengubah alamat (di awal siklus).

Kemudian Slave menambah alamat ini pada setiap transfer sehingga data dari transfer berikutnya disimpan di lokasi berikutnya yang lebih tinggi.

Klausa 1.3.1.3.5 – 1.3.1.3.6

1.3.1.3.5 multiplexed cycle : siklus multipleks

siklus DTB yang mentransfer informasi alamat dan/atau informasi data menggunakan bus alamat dan data. Siklus multipleks digunakan dalam empat kasus :

- • a) A64 — bus alamat lengkap dan bus data lengkap digabungkan untuk membuat alamat 64 bit.

- • b) MBLT – bus alamat lengkap dan bus data lengkap digabungkan untuk membuat kata data 64 bit.

- • c) A40 — Bus alamat 24 bit penuh dan bus data 16 bit penuh pada konektor P1/J1 digabungkan untuk membuat alamat 40 bit. Mode ini sangat berguna untuk board (papan) 3U yang hanya memiliki konektor J1.

- • d) MD32 — 16 baris alamat yang lebih rendah dan 16 baris data yang lebih rendah digabungkan untuk membuat kata data 32 bit. Mode ini sangat berguna untuk modul 3U.

Lalu, Siklus multipleks digunakan dalam transfer dasar dan transfer blok.

ransfer dasar A64 dan A40 mendukung transfer 1 byte, 2 byte, dan 4 byte. Selain itu siklus MBLT mendukung transfer 8 byte.

Siklus Multiplexed akan memiliki fase Alamat yang terpisah dari fase Data.

Fase Alamat dapat mencakup (yaitu siklus A64 dan A40) atau mungkin tidak termasuk (yaitu siklus A32, A24) penggunaan bus Data.

Fase Data dapat mencakup (siklus MBLT, MD32) atau mungkin tidak mencakup (yaitu siklus D32, D16, D08(OE)) penggunaan bus Alamat.

Transfer blok multipleks dapat memiliki 1 hingga 256 transfer antara Master dan Slave. Dengan transfer 8 byte, hingga 2.048 byte dapat ditransfer dalam satu blok.

1.3.1.3.6 read-modify-write cycle : siklus baca-ubah-tulis

siklus DTB yang digunakan untuk membaca dari, dan menulis ke, lokasi Slave tanpa mengizinkan Master lain untuk mengakses lokasi itu

Siklus ini paling berguna dalam sistem multiprosesor di mana lokasi memori tertentu digunakan untuk menyediakan fungsi semaphore.

Klausa 1.3.1.3.7 – 1.3.1.3.9

1.3.1.3.7 address-only cycle : siklus alamat-saja

siklus DTB yang terdiri dari siaran alamat, tetapi tidak ada transfer data

Budak tidak mengakui siklus ALAMAT-HANYA dan Master mengakhiri siklus tanpa menunggu pengakuan.

Tidak ada strobe data atau strobe pengakuan yang ditegaskan dalam siklus ALAMAT-HANYA.

1.3.1.3.8 address-only-with-handshake cycle : siklus alamat-saja-dengan-jabat tangan

siklus DTB yang terdiri dari siaran alamat, tetapi tidak ada transfer data

Slave yang dialamatkan merespon dengan cara yang sama seperti siklus akses standar.

1.3.1.3.9 interrupt acknowledge cycle : mengganggu siklus pengakuan

siklus DTB, yang diprakarsai oleh Interrupt Handler, yang membaca STATUS/ID dari Interrupter

Interrupt Handler menghasilkan siklus ini setiap kali mendeteksi permintaan interupsi dari Interrupter dan memiliki kontrol DTB.

1.3.2 Basic VMEbus structure : Struktur dasar VMEbus

Sistem antarmuka VMEbus terdiri dari logika antarmuka backplane, empat kelompok jalur sinyal yang disebut bus, dan kumpulan modul fungsional yang dapat dikonfigurasi sesuai kebutuhan.

Modul fungsional berkomunikasi satu sama lain menggunakan jalur sinyal backplane.

Modul fungsional yang didefinisikan dalam dokumen ini digunakan sebagai kendaraan untuk diskusi protokol bus dan tidak perlu dianggap sebagai kendala untuk desain logika.

Misalnya, perancang mungkin memilih untuk merancang logika yang berinteraksi dengan VMEbus dengan cara yang dijelaskan, tetapi menggunakan sinyal onboard yang berbeda, atau memantau sinyal VMEbus lainnya.

Board (papan) VMEbus mungkin dirancang untuk memasukkan kombinasi modul fungsional apa pun yang ditentukan oleh standar ini.

Struktur fungsional VMEbus dapat dibagi menjadi empat kategori.

Masing-masing terdiri dari bus dan modul fungsional terkait yang bekerja sama untuk melakukan tugas tertentu.

Gambar 2 menunjukkan modul dan bus fungsional VMEbus.

Setiap kategori diringkas secara singkat di bawah ini.

Klausa 1.3.2.1 – 1.3.2.4

1.3.2.1 data transfer : transfer data

perangkat mentransfer data melalui Data Transfer Bus (DTB), yang berisi jalur data dan alamat serta sinyal kontrol terkait

Modul fungsional yang disebut Master, Slave, Interrupters, dan Interrupt Handler menggunakan DTB untuk mentransfer data antara satu sama lain.

Dua modul lain, yang disebut Bus Timer dan IACK Daisy-Chain Driver juga membantu mereka dalam proses ini.

1.3.2.2 DTB arbitration : arbitrase DTB

karena sistem VMEbus dapat dikonfigurasi dengan lebih dari satu Master atau Interrupt Handler, sarana disediakan untuk mentransfer kontrol DTB di antara mereka secara teratur dan untuk menjamin bahwa hanya satu Master yang mengontrol DTB pada waktu tertentu.

Modul Bus Arbitrase (Pemohon dan Arbiter) mengoordinasikan transfer kontrol

1.3.2.3 priority interrupt : interupsi prioritas

kemampuan interupsi prioritas dari VMEbus menyediakan sarana di mana perangkat dapat meminta layanan dari Interrupt Handler

Permintaan interupsi ini dapat diprioritaskan menjadi maksimal tujuh level. Interrupter dan Interrupt Handler menggunakan jalur sinyal Priority Interrupt Bus.

1.3.2.4 utilities : keperluan

jam periodik, inisialisasi, dan deteksi kegagalan disediakan oleh Bus Utilitas

Ini termasuk jalur jam sistem tujuan umum, jalur reset sistem, jalur kegagalan sistem, a.c. garis gagal, dan dua garis serial. Utilitas juga mencakup pin daya dan ground.

ISO/IEC 15776:2001 Klausa 1

1. General : Umum

Dikarenakan isi Klausa 1 terlalu panjang, maka pembaca bisa melanjutkan ke artikel lanjutan dari standarku.com berikut :

- ISO IEC 15776 Klausa 1.4 – 1.7

Penutup

Demikian artikel dari standarku.com mengenai Standar ISO IEC 15776.

Mohon saran dari pembaca untuk kelengkapan isi artikel ini, silahkan saran tersebut dapat disampaikan melalui kolom komentar.

Baca artikel lain :

- International Organization for Standardization

- Memahami apa itu Standar ISO

- Memahami Standard atau Standar

Sumber referensi :

- https://www.iso.org/obp/ui/#iso:std:iso-iec:15776:ed-1:v1:en:sec:C

- https://www.iso.org/standard/28939.html