ISO IEC 15776 Klausa 1.4 – 1.7 adalah Standar Internasional mengenai VME64bus Specification, yang mendefinisikan sistem antarmuka yang digunakan untuk menghubungkan mikroprosesor, penyimpanan data, dan perangkat kontrol periferal.

Artikel ini merupakan lanjutan dari artikel sebelumnya berikut :

- ISO IEC 15776 VME64bus Specification

- ISO IEC 15776 Klausa 1.1 – 1.3

Standar ISO 15776 Klausa 1.4 – 1.7

1.4 VMEbus specification diagrams : diagram spesifikasi VMEbus

Sebagai bantuan untuk mendefinisikan atau menggambarkan operasi VMEbus, beberapa jenis diagram digunakan, termasuk:

• a) Diagram waktu yang menunjukkan hubungan waktu antara transisi sinyal.

Waktu yang terlibat akan memiliki batas minimum dan/atau maksimum yang terkait dengannya.

Beberapa waktu yang ditentukan pada diagram ini menentukan perilaku logika antarmuka backplane, sementara waktu lain menentukan perilaku modul fungsional yang saling terkait.

• b) Diagram urutan yang mirip dengan diagram waktu tetapi hanya menunjukkan hubungan waktu yang saling terkait dari modul fungsional.

Diagram ini dimaksudkan untuk menunjukkan urutan peristiwa, bukan untuk menentukan waktu yang terlibat.

Misalnya, diagram urutan mungkin menunjukkan bahwa modul A tidak dapat menghasilkan transisi sinyal B sampai modul C mendeteksi generasi transisi sinyal D.

• c) Diagram alir yang menunjukkan aliran peristiwa seperti yang akan terjadi selama operasi VMEbus.

Peristiwa dinyatakan dalam kata-kata dan hasil dari interaksi dua atau lebih modul fungsional.

Diagram alir menggambarkan operasi VMEbus secara berurutan dan, pada saat yang sama, menunjukkan interaksi modul fungsional.

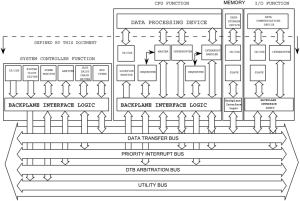

Gambar 2 — Functional modules and buses : Modul dan bus fungsional

ISO IEC 15776 Klausa 1.5 Specification terminology : Terminologi spesifikasi

Untuk menghindari kebingungan, dan untuk memperjelas persyaratan kepatuhan, banyak paragraf dalam dokumen ini diberi label dengan kata kunci yang menunjukkan jenis informasi yang dikandungnya.

Kata kunci atau keywords tercantum di bawah ini :

- RULE : ATURAN

- RECOMMENDATION : REKOMENDASI

- SUGGESTION : SARAN

- PERMISSION : IZIN

- OBSERVATION : PENGAMATAN

Teks apa pun yang tidak diberi label dengan salah satu kata kunci ini menjelaskan struktur atau operasi VMEbus.

Hal ini ditulis baik dalam deskriptif atau gaya naratif.

Kata kunci ini digunakan sebagai berikut:

RULE chapter.number : ATURAN bab.nomor

Aturan membentuk kerangka dasar spesifikasi VMEbus.

Mereka kadang-kadang dinyatakan dalam bentuk teks dan kadang-kadang dalam bentuk Gambar, tabel, atau gambar.

Semua aturan VMEbus HARUS diikuti untuk memastikan kompatibilitas antara desain VMEbus. Aturan dicirikan oleh gaya imperatif.

Kata-kata huruf besar HARUS dan TIDAK HARUS dicadangkan secara eksklusif untuk menyatakan aturan dalam dokumen ini dan tidak digunakan untuk tujuan lain apa pun.

RECOMMENDATION chapter.number : REKOMENDASI chapter.number

Di mana pun rekomendasi muncul, desainer akan bijaksana untuk menerima saran yang diberikan. Melakukan sebaliknya dapat mengakibatkan beberapa masalah canggung atau kinerja yang buruk.

Sementara VMEbus telah dirancang untuk mendukung sistem kinerja tinggi, dimungkinkan untuk merancang sistem VMEbus yang mematuhi semua aturan, tetapi memiliki kinerja yang buruk.

Dalam banyak kasus, seorang desainer membutuhkan tingkat pengalaman tertentu dengan VMEbus untuk merancang board (papan) yang memberikan kinerja terbaik.

Rekomendasi yang ditemukan dalam dokumen ini didasarkan pada pengalaman semacam ini dan diberikan kepada desainer untuk mempercepat perjalanan kurva pembelajaran mereka.

SUGGESTION chapter.number : SUGGESTION chapter.number

Dalam spesifikasi VMEbus, saran berisi saran yang bermanfaat tetapi tidak vital. Pembaca didorong untuk mempertimbangkan saran sebelum membuangnya.

Beberapa keputusan desain yang perlu dibuat dalam merancang board (papan) VMEbus sulit sampai pengalaman diperoleh dengan VMEbus.

Saran disertakan untuk membantu seorang desainer yang belum mendapatkan pengalaman ini.

Beberapa saran berkaitan dengan merancang board (papan) yang dapat dengan mudah dikonfigurasi ulang untuk kompatibilitas dengan board (papan) lain, atau dengan merancang board (papan) untuk membuat pekerjaan sistem debugging lebih mudah.

PERMISSION chapter.number : Bab PERMISSION.number

Dalam beberapa kasus aturan VMEbus tidak secara khusus melarang pendekatan desain tertentu, tetapi pembaca mungkin bertanya-tanya apakah pendekatan itu mungkin melanggar semangat aturan, atau apakah itu mungkin menyebabkan beberapa masalah halus.

Izin meyakinkan pembaca bahwa pendekatan tertentu dapat diterima dan tidak akan menimbulkan masalah.

Kata huruf besar MAY dicadangkan secara eksklusif untuk menyatakan izin dalam dokumen ini dan tidak digunakan untuk tujuan lain apa pun.

OBSERVATION chapter.number : OBSERVASI bab.nomor

Pengamatan tidak menawarkan saran khusus. Mereka :

- biasanya mengikuti secara alami dari apa yang baru saja dibahas.

- menguraikan implikasi dari aturan VMEbus tertentu dan membawa perhatian pada hal-hal yang mungkin diabaikan.

- juga memberikan alasan di balik aturan tertentu, sehingga pembaca mengerti mengapa aturan itu harus diikuti.

1.5.1 Signal line states

Spesifikasi VMEbus menjelaskan protokolnya dalam hal level dan transisi pada jalur bus.

Garis sinyal selalu diasumsikan berada di salah satu dari dua level atau dalam transisi antara level ini. Setiap kali istilah “tinggi” digunakan, ini mengacu pada level tegangan TTL yang tinggi.

Istilah “rendah” mengacu pada level tegangan TTL yang rendah.

Garis sinyal “dalam transisi” ketika tegangannya bergerak di antara level-level ini.

(Lihat klausa 6 untuk ambang tegangan yang digunakan pada VMEbus.)

Ada dua kemungkinan transisi yang dapat muncul pada garis sinyal, dan ini disebut “edge (tepi)”.

- Rising edge adalah waktu di mana level sinyal membuat transisi dari level rendah ke level tinggi.

- Falling edge adalah waktu di mana level sinyal membuat transisi dari level tinggi ke level rendah.

Beberapa spesifikasi bus menentukan waktu naik dan turun maksimum atau minimum untuk edge (tepi) ini.

Masalah dengan melakukan ini adalah bahwa desainer board (papan) memiliki kontrol yang sangat sedikit atas waktu ini.

Jika backplane dibebani berat, waktu naik dan turun akan lama. Jika dimuat dengan ringan, waktu ini mungkin singkat.

Bahkan jika desainer tahu berapa beban maksimum dan minimum, mereka masih perlu menghabiskan waktu di lab, bereksperimen untuk mengetahui driver mana yang akan memberikan waktu naik dan turun yang dibutuhkan.

Faktanya, waktu naik dan turun adalah hasil dari serangkaian interaksi kompleks yang melibatkan impedansi garis sinyal dari bidang belakang, penghentiannya, impedansi sumber driver, dan pemuatan kapasitif dari garis sinyal.

Untuk menukar semua faktor ini, perancang board (papan) harus mempelajari teori saluran transmisi, serta parameter spesifik tertentu dari driver dan penerima yang biasanya tidak ditemukan di sebagian besar lembar data pabrikan.

standar VMEbus

Menyadari semua ini, standar VMEbus tidak menentukan waktu naik dan turun.

Sebaliknya, ini menentukan karakteristik listrik untuk driver dan penerima dan menentukan desain backplane.

Ini juga memberi tahu desainer bagaimana pemuatan bus kasus terburuk akan mempengaruhi penundaan propagasi driver ini sehingga mereka dapat memastikan bahwa waktu VMEbus terpenuhi sebelum membangun board (papan).

Jika desainer VMEbus mengikuti panduan penundaan propagasi ini, board (papan) mereka akan beroperasi dengan andal dengan board (papan) kompatibel VMEbus lainnya dalam kondisi terburuk.

Kinerja sistem dipengaruhi oleh waktu naik salah satu sinyal kontrol kolektor terbuka. Untuk meningkatkan kinerja sistem, konsep sinyal pembatalan telah diperkenalkan.

Sinyal pembatalan adalah output tipe kolektor terbuka yang awalnya didorong tinggi dan kemudian dilepaskan kembali ke mode kolektor terbuka dalam waktu singkat.

1.5.2 Use of the asterisk (*) : Penggunaan tanda bintang (*)

Untuk membantu menentukan penggunaan, mnemonik sinyal memiliki akhiran asterisk jika diperlukan.

- a) Tanda bintang (*) setelah nama sinyal dari sinyal yang levelnya signifikan menunjukkan bahwa sinyal itu benar atau valid ketika sinyalnya rendah.

- b) Tanda bintang (*) setelah nama sinyal sinyal yang signifikan edge (tepi) menunjukkan bahwa tindakan yang diprakarsai oleh sinyal itu terjadi pada transisi tinggi ke rendah.

OBSERVATION 1.1 : PENGAMATAN 1.1

Tanda bintang tidak sesuai untuk SYSCLK garis jam yang berjalan secara tidak sinkron. Tidak ada hubungan fase tetap antara garis jam ini dan waktu VMEbus lainnya.

1.5.3 Keyword numbering : Penomoran kata kunci

Standar ini didasarkan pada standar sebelumnya.

Untuk mempertahankan penomoran kata kunci, kata kunci baru (aturan, rekomendasi, saran, izin, pengamatan) telah diberi nomor mulai dari nomor terakhir yang tersedia.

Oleh karena itu, kata kunci seperti yang disajikan di seluruh standar ini tidak diperlukan secara berurutan.

Lihat indeks referensi silang kata kunci untuk menentukan di mana kata kunci tertentu dirujuk.

ISO IEC 15776 Klausa 1.6 Protocol specification : Spesifikasi protokol

Ada dua lapisan protokol VMEbus.

Lapisan VMEbus terendah, yang disebut lapisan akses backplane, terdiri dari logika antarmuka backplane, modul Bus Utilitas, dan modul Bus Arbitrase.

Lapisan transfer data VMEbus, terdiri dari modul Bus Transfer Data dan Bus Interupsi Prioritas.

Gambar 2 menunjukkan layering ini.

OBSERVATION 1.2 : PENGAMATAN 1.2

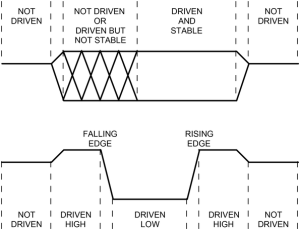

Jalur sinyal yang digunakan oleh modul lapisan transfer data membentuk kelas khusus karena digerakkan oleh modul yang berbeda pada waktu yang berbeda.

Mereka didorong dengan driver garis yang dapat dihidupkan dan dimatikan di setiap board (papan) berdasarkan sinyal yang dihasilkan di lapisan akses backplane.

Sangat penting bahwa waktu menghidupkan dan mematikan mereka dikontrol dengan hati-hati untuk mencegah dua pengemudi mencoba mengemudikan jalur sinyal yang sama ke level yang berbeda.

Notasi diagram pengaturan waktu khusus digunakan dalam dokumen ini untuk menentukan waktu nyala dan matinya. Hal ini ditunjukkan pada Gambar 3.

Ada dua jenis protokol dasar yang digunakan pada VMEbus: protokol loop tertutup dan protokol loop terbuka.

Protokol loop tertutup menggunakan sinyal bus yang saling terkait sementara protokol loop terbuka menggunakan sinyal bus siaran.

1.6.1 Interlocked bus signals : Sinyal bus yang saling bertautan

Sinyal bus yang saling bertautan dikirim dari modul tertentu ke modul spesifik lainnya. Sinyal diakui oleh modul penerima. Hubungan saling terkait ada antara dua modul sampai sinyal diakui.

Misalnya, Interrupter dapat mengirim permintaan interupsi yang dijawab kemudian dengan sinyal interupsi yang diakui (tidak ada batas waktu yang ditentukan oleh spesifikasi VMEbus).

Interrupter tidak menghapus permintaan interupsi sampai Interrupt Handler mengakuinya.

Sinyal bus yang saling terkait mengoordinasikan fungsi internal sistem VMEbus, sebagai lawan dari interaksi dengan rangsangan eksternal.

Setiap sinyal yang saling bertautan memiliki modul sumber dan modul tujuan dalam sistem VMEbus.

Strobo alamat dan strobo data merupakan sinyal interlocking yang sangat penting.

Mereka saling terkait dengan transfer data yang mengakui dan sinyal kesalahan bus dan mengoordinasikan transfer alamat dan data yang merupakan dasar untuk semua aliran informasi antar modul di lapisan transfer data.

1.6.2 Broadcast bus signal : Sinyal bus siaran

Modul menghasilkan sinyal siaran sebagai respons terhadap suatu peristiwa.

Tidak ada protokol untuk mengakui sinyal siaran.

Sebaliknya, siaran dipertahankan untuk waktu yang ditentukan minimum, cukup lama untuk memastikan bahwa semua modul yang sesuai mendeteksi sinyal.

Sinyal siaran dapat diaktifkan kapan saja, terlepas dari aktivitas lain apa pun yang terjadi di bus. Mereka masing-masing dikirim melalui jalur sinyal khusus.

Beberapa contoh adalah sistem reset dan a.c. garis kegagalan.

Jalur sinyal ini tidak dikirim ke modul tertentu, tetapi mengumumkan kondisi khusus untuk semua modul.

Gambar 3 — Signal timing notation : Notasi waktu sinyal

ISO IEC 15776 Klausa 1.7 System examples and explanations : Contoh dan penjelasan sistem

Sebuah spesifikasi protokol menjelaskan, secara rinci, perilaku berbagai modul fungsional. Ini membahas bagaimana modul merespons sinyal tanpa mengatakan dari mana sinyal itu berasal.

Karena itu, spesifikasi protokol tidak memberikan gambaran lengkap kepada pembaca tentang apa yang terjadi di atas bus.

Untuk membantu pembaca, spesifikasi VMEbus memberikan contoh operasi VMEbus yang khas. Setiap contoh menunjukkan satu kemungkinan urutan kejadian; urutan lain juga mungkin.

Dalam memberikan contoh-contoh ini, ada bahaya bahwa pembaca akan menganggap bahwa urutan yang ditunjukkan dalam contoh adalah satu-satunya yang sah.

Untuk membantu pembaca menghindari jebakan ini, semua contoh diberikan dalam gaya naratif, menggunakan present tense.

Ini berbeda dengan gaya imperatif yang digunakan saat memberikan aturan untuk kepatuhan dengan spesifikasi VMEbus.

Penutup

Demikian artikel dari standarku.com mengenai Standar ISO IEC 15776.

Mohon saran dari pembaca untuk kelengkapan isi artikel ini, silahkan saran tersebut dapat disampaikan melalui kolom komentar.

Baca artikel lain :

- International Organization for Standardization

- Memahami apa itu Standar ISO

- Memahami Standard atau Standar

Sumber referensi :

- https://www.iso.org/obp/ui/#iso:std:iso-iec:15776:ed-1:v1:en:sec:C

- https://www.iso.org/standard/28939.html